-

Notifications

You must be signed in to change notification settings - Fork 1.4k

Correct computation of SPI baud rate register value, and allow for the value to be 0. #560

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Correct computation of SPI baud rate register value, and allow for the value to be 0. #560

Conversation

deshipu

left a comment

deshipu

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Thank you very much for this!

|

I thought of something better overnight, which is to accept any frequency and just give the nearest one. So it would never throw an exception for a bad frequency. Then I will also add an attribute to return the actual frequency. If you like that, hold off on the merge and I'll push something new. |

|

Yes, I think that would be the best approach — I think many APIs behave that way. However, I don't have the rights to merge anything here. I'm still more than happy to review and test it, of course. |

|

git breakage: hold on until I fix the commits. |

080c9ff to

69924ac

Compare

all: Add .frequency read-only property for busio.SPI to return actual frequency. Fix esp8266/posix_helpers.c, which was not up to date for the new long-lived/short-lived heap allocation scheme.

69924ac to

e550b02

Compare

|

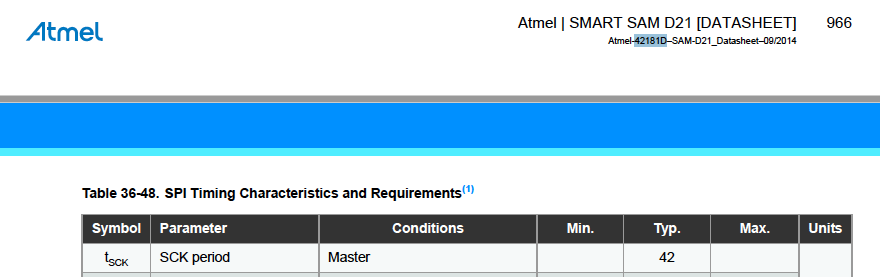

please note, 24 mhz is outside the spec for the SERCOM max clock speed arduino/ArduinoCore-samd#147 |

|

We can keep the default in all the libraries at 12MHz, but a 24MHz SPI is really a huge improvement with displays (and only slightly out of the 20MHz spec for them), and I think it's worth it to be able to set it when one knows what they are doing. |

|

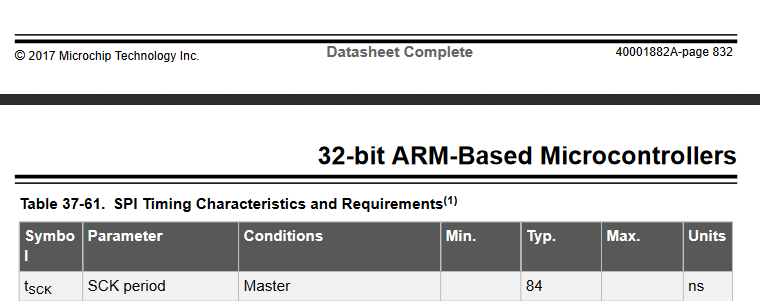

arduino/ArduinoCore-samd#147 (comment) mentions that the datasheet gives a Typical value of 12MHz, and doesn't specify a Max. The SAMD51 datasheet doesn't specify a Max either. I can allow it but add a warning to the API documentation. Would that be OK? |

|

yep that sounds good to me! |

tannewt

left a comment

tannewt

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Looks great! Its backwards compatible too.

|

Additional clarification:

|

|

@joseangeljimenez hiya can you show us where you see tSCK of 42 ns? The one I just downloaded from microchip shows 84: 12 MHz was not chosen due to air-wiring/breadboard constraints. It was definitely the 'official' max frequency for proper SPI operation from Atmel :) I don't mind allowing 24 MHz but its not officially supported :) |

|

@ladyada I am really sorry for the confusion! I checked this using my old locally stored datasheet rev 42181D (dated 09/2014), where it states tSCK (typ.) = 42 ns. You are absolutely right that the newest datasheet shows 84 ns. I have been working with the SAMD21 for several years now and designed several boards using SPI clocks up to 24 MHz, with a proper layout (5-6 mils narrow, short tracks PCB). I guess that Atmel revised (conservatively) the typical value of tSCK. |

Fixes #464. Corrects baud rate computation to match formula. Allow baud register value to be 0, which allows maximum rate. On both M0 and M4, with SPI SERCOM clocked at 48 MHz, I can get 24Mhz SPI clock pulses now, as verified by my Saleae.

Previous error checking used to error out above a maximum SPI frequency. That was not intentional, but was due to checking for the baud register value being 0. That is no longer the case: 0 is a legitimate value. The frequency can be arbitrarily high, and you'll just get the highest available frequency from the clocked SERCOM.

I didn't add anything that returns you the actual frequency, but I could.